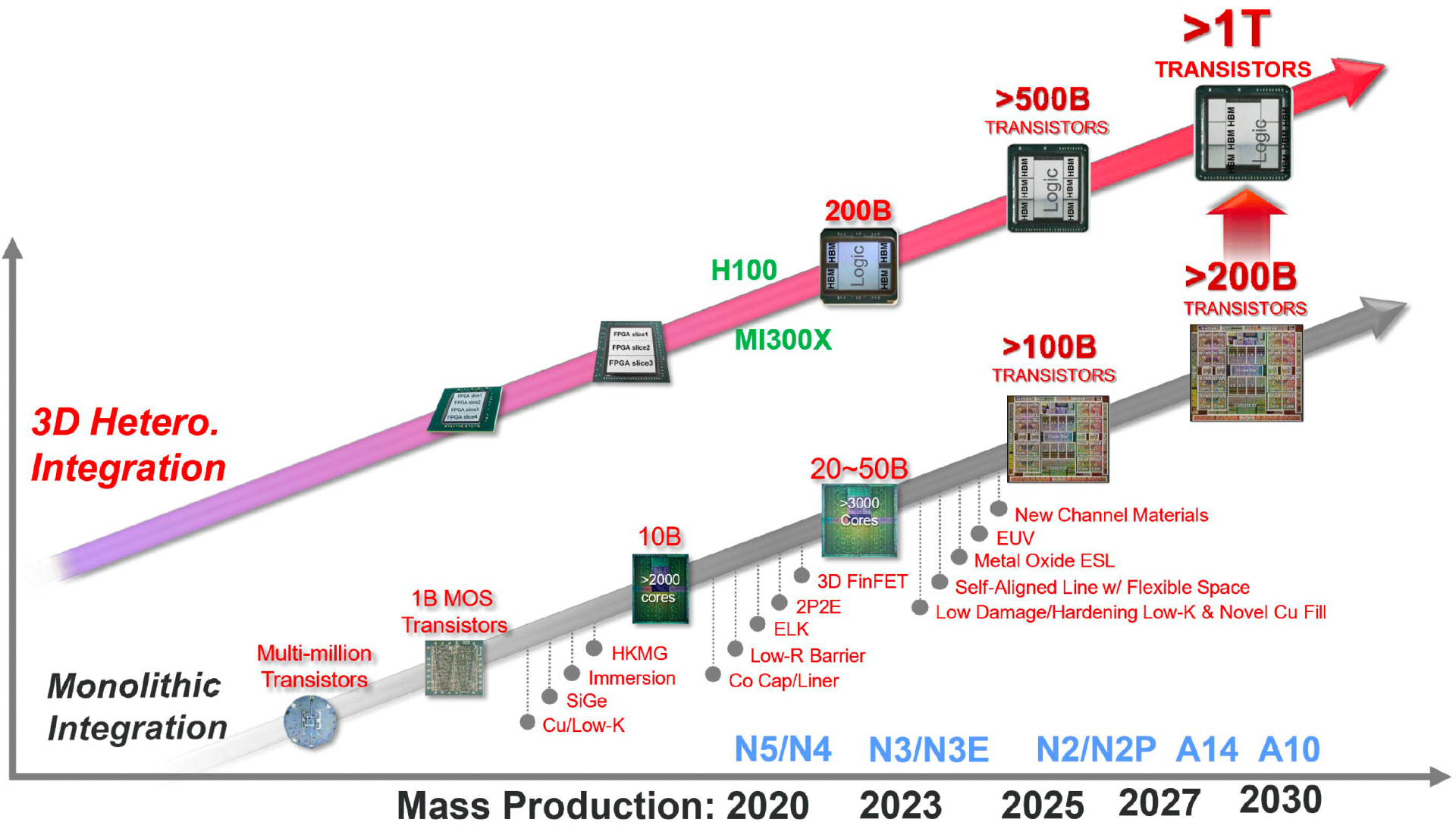

TSMC планирует поместить более 1 трлн транзисторов в 3D-упаковку к 2030-му. 5-кратный прирост

TSMC очертила планы поместить более 1 трлн транзисторов в 3D-упаковке и 200 млрд в монолитных чипах к 2030 году. На конференции IEDM 2023 компания показала дорожную карту относительно того, каким должен быть ее полупроводниковый «портфель», и, похоже, тайваньский гигант имеет амбициозные планы на конец этого десятилетия.

Исходя из обнародованной дорожной карты, TSMC уверена, что ее техпроцессы находятся на правильном пути: дебют техпроцессов TSMC N2 и N2P состоится в 2025-2027 годах, а передовые техпроцессы A10 (1 нм) и A14 (1,4 нм) запланированы на 2027-2030 год. Помимо уменьшения технологических процессов, TSMC планирует добиться значительных успехов и в других полупроводниковых технологиях, установив ориентиры для отрасли, сообщает Wccftech.

Интереснее то, что тайваньский гигант раскрыл достижения в двух ключевых секторах полупроводниковой индустрии – монолитных конструкциях и 3D гетероинтеграции (или чиплетных конструкциях). Промышленность действительно смещается в сторону чиплетной конфигурации, поскольку они предлагают модульность и экономические преимущества.

AMD использует дизайн микросхем TSMC для новейших потребительских чипов, микросхем для центров обработки данных, а теперь и для новейших чипов ускорителей MI300. Intel также выпустила свои Meteor Lake, являющиеся первой разработкой синей команды для потребительских платформ, намекая на то, что будущее за чиплетами, и TSMC на шаг впереди. Сама Intel для Meteor Lake пользуется технологичными процессами TSMC. Компания прогнозирует, что к 2030 году 3D-гетероинтеграция достигнет колоссального объема в «один трлн транзисторов».