Держись, Intel. Samsung удалось создать 3-нм кристалл памяти SRAM плотностью 256 Мбит с использованием транзисторов MBCFET

Об успехах в освоении следующего шага технологических норм (3 нм) и литографических технологий Samsung Foundry рассказала в рамках Международной конференции IEEE по твердотельным схемам (ISSCC) — там же был продемонстрирован прототип 3-нм кристалла памяти SRAM плотностью 256 Мбит с использованием транзисторов MBCFET.

На сегодняшний день наиболее передовым техпроцессом, освоенным TSMC и Samsung в серийном производстве, является 5-нанометровый. Важно оговорить, что технологии Samsung 5LPP и TSMC N5 — разные и не совместимы между собой, хотя и обе основаны на литографии в жестком ультрафиолетовом диапазоне (EUV). Напомним, TSMC выпускает для Apple 5-нм чипы A14 и M1, а Samsung производит новейшие мобильные SoC Snapdragon 888 и Samsung Exynos 2100. Следующий этап технологического развития Samsung Foundry — 3-нм с использованием новой архитектуры транзисторов gate-all-around FET (GAAFET).

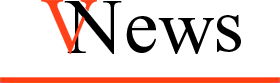

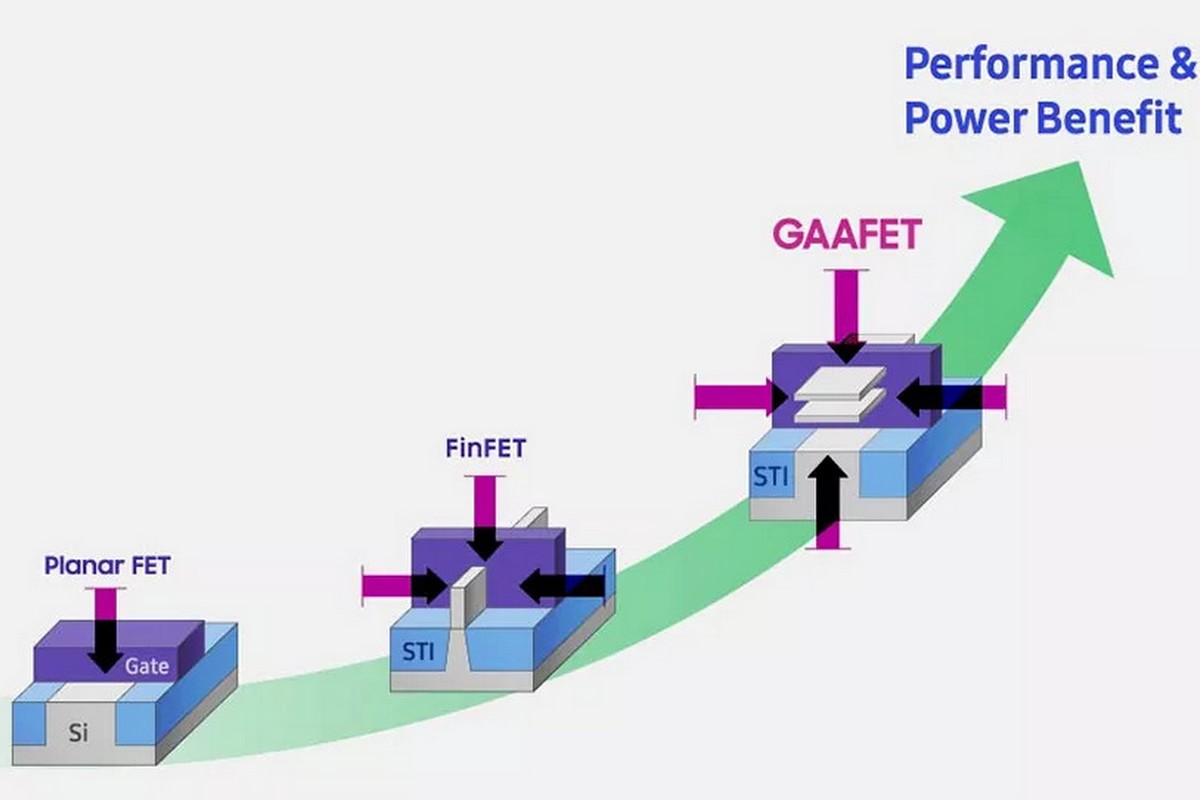

Для справки: архитектура GAAFET, идущая на смену нынешней FinFET, разрабатывается организацией, в которую входят IBM, Globalfoundries и Samsung, с 2000 года. Именно она должна помочь преодолеть физические ограничения по масштабированию МОП. Главная особенность GAAFET — кольцевые затворы (отсюда и название gate-all-around FET). Каналы транзисторов GAAFET представляют собой нанопровода (они сформированы из нескольких горизонтальных кремниевых «нанолистов»). В то же время канал FinFET транзистора под затвором представляет собой монолитную вертикальную конструкцию «плавник», что и накладывает ограничения по масштабированию.

У Samsung собственная реализация технологии GAAFET, которая носит маркетинговое название Multi-Bridge-Channel FET (MBCFET). На самом деле MBCFET отличается от GAAFET не только названием, но и технически: в случае реализации Samsung каналы выполнены виде плоских «мостиков», а не «проводков». Наглядное представление о различиях дает изображение ниже.

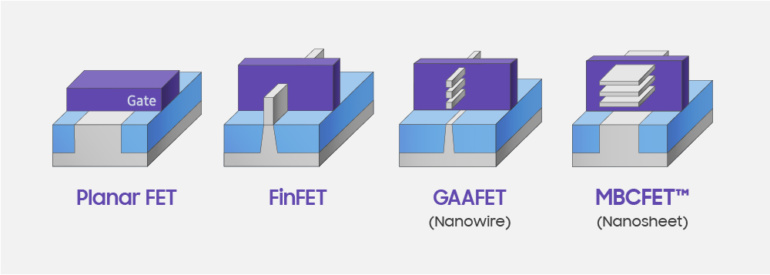

Особенностью MCBFET является возможность размещения транзисторов стопкой с целью повышения плотности компоновки и экономией места по сравнению с FinFET. Кроме того, для MCBFET характерна гибкость — можно менять ширину транзисторов в стеке в соответствии с конкретными техническими требования.

То есть, можно оптимизировать технологию по энергопотреблению или быстродействию.

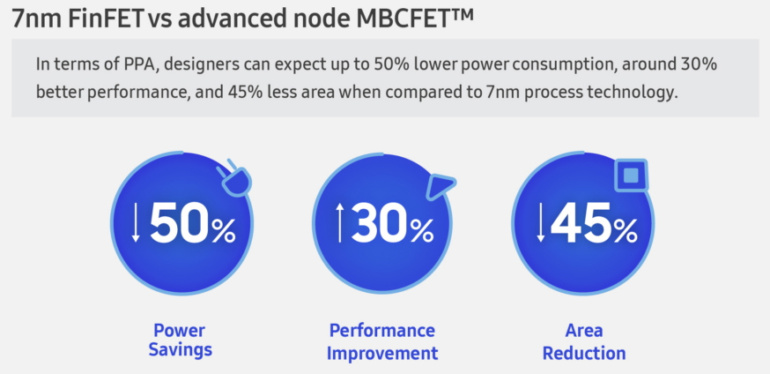

Если же говорить о показателях производительности и энергопотребления, по сравнению с 7LPP, будущий технологический узел 3GAE (потенциальный 3LPP), как ожидается, позволит уменьшить площадь микросхемы на 45% при одновременном снижении потребления энергии на 50% и повышении производительности на 30%.

В рамках ISSCC сотрудники Samsung Foundry продемонстрировали прототип микросхемы SRAM площадью 56 мм², произведенный по 3-нм технологии с транзисторами MBCFET. Это первый чип 3GAE, подтверждающий возможность использовать технологии для выпуска микросхем SRAM.

В рамках ISSCC сотрудники Samsung Foundry продемонстрировали прототип микросхемы SRAM площадью 56 мм², произведенный по 3-нм технологии с транзисторами MBCFET. Это первый чип 3GAE, подтверждающий возможность использовать технологии для выпуска микросхем SRAM.

На самом деле Samsung разработала два варианта схемы: в одном использовались транзисторы с более широкими каналами для передаточных затворов и стягивающих резисторов, а во втором — транзисторы с более широкими каналами для передаточных затворов и транзисторы с более узкими каналами для стягивающих резисторов. Во втором случае Samsung удалось снизить рабочее напряжение на 230 мВ по сравнению с классическим кристаллом SRAM с транзисторами FinFET.

Изначально Samsung планировала начать серийный выпуск 3-нанометровой продукции в 2021 году, но из-за пандемии отложила старт производства 3-нм полупроводников на 2022 год. Тайваньский производитель TSMC рассчитывает начать пробный выпуск 3-нм продукции уже в этом году. Будет интересно посмотреть, кто в итоге выйдет победителем из этой гонки и первым наладит выпуск 3-нм продукции.