TSMC: кэш SRAM для CPU и GPU достиг пределов масштабирования – кэш-память процессоров перестанет стремительно расти, а разработка подорожает

В этом году 68-я ежегодная конференция IEEE International Electron Devices Meeting (IEDM) развернулась вернулась в полную силу, собрав в очном порядке почти 1500 инженеров со всего мира в Сан-Франциско.

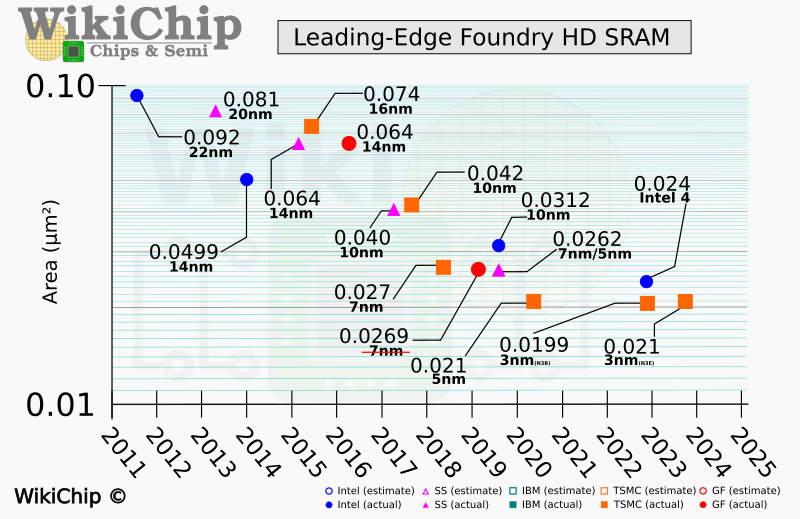

Среди множества материалов академического и прикладного характера, касающихся развития отрасли, наибольший резонанс произвел доклад TSMC о дальнейшей перспективае масштабирования плотности кэш-памяти SRAM. Если коротко – оно остановилось. В то время, как системная логика процессоров все еще имеет резерв масштабирования, используемые в промышленности технологии более не способны значительно увеличить плотность SRAM.

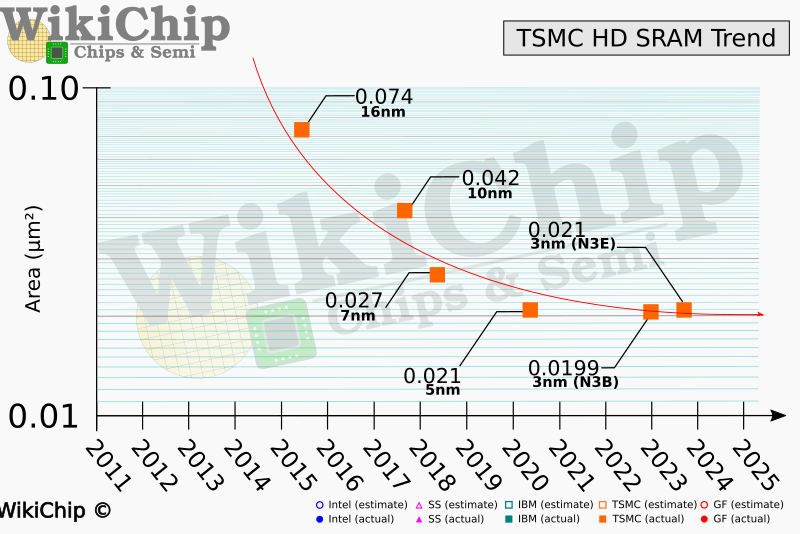

На конференции TSMC рассказала своем исходном базовом узле N3B и об улучшенном его варианте N3E. Что интересно, для нового узла N3E размер битовой ячейки SRAM высокой плотности совсем не уменьшился. Площадь битовой ячейки составляет 0,021 мкм² – ровно столько же, как у узла N5. Вариант N3B, который, как ожидается, не будет использоваться большинстве продуктов, имеет меньшую ячейку SRAM, однако его 0,0199 мкм² – это сокращение всего на 5% по сравнению с техпроцессом N5. Что касается приблизительной плотности памяти, для N3E она составляет примерно 31,8 МБ/мм² и может увеличиться до 33,55 МБ/мм² или на 1,75 МБ/мм².

Чтобы представить темпы и возможности развития процессоров в перспективе, заметим,что в то время как N3B и N3E обеспечивают 1,6-кратное и 1,7-кратное масштабирование транзисторов на уровне микросхемы, масштабирование SRAM составляет всего 1-1,05 раза. По прежнему можно ожидать, что TSMC продолжит создание более плотных битовых ячеек SRAM для N3, но существенных изменений на этом пути не будет.

Замедление масштабирования SRAM не ограничивается только TSMC, проблема существует уже довольно давно. Intel все еще способна уменьшать плотность ячеек SRAM, однако недавно в недавно анонсированном техпроцессе Intel 4 масштабирование SRAM замедлилось до 0,7-0,8 раза.

Влияние остановки масштабирования SRAM на разработку процессоров

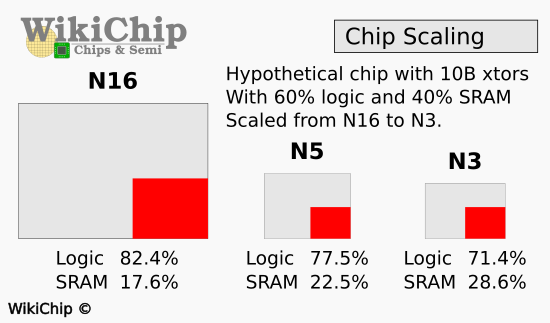

В настоящее время единственной жизнеспособной альтернативой масштабированию SRAM является просто увеличение объема кэш-памяти – ожидается, что SRAM будет занимать больше места на кристалле микрочипа. Это может увеличить стоимость производства процессоров и помешать некоторым архитектурам стать настолько маленькими, насколько они могли бы быть. Физическое ограничение масштабирования кэша становится фактором, более существенно влияющим на разработку будущих архитектур.

Большинство процессоров полагаются на кэш-память, как на высокоскоростное решение для хранения данных с минимальным временем доступа благодаря их стратегическому расположению рядом с вычислительными ядрами. Наличие быстрого и доступного хранилища может значительно повысить производительность обработки и сократить время, затрачиваемое ядрами на выполнение своей работы. Соответственно замедления развития технологии кэширования накладывает ограничение на рост быстродействия.

Дальнейшие перспективы и альтернативы улучшения кэш-памяти

Некоторые исследовательские институты, такие как Imec, уже представили ячейки SRAM с более высокой плотностью. В прошлом году на выставке IEDM 2021 компания Imec представила плотность SRAM около 60 МБмм², что примерно в два раза превышает сегодняшнюю плотность на гипотетическом узле свыше 2 нм – с использованием разветвленных транзисторов и усовершенствованной схемы двустороннего межсоединения.

Помимо SRAM, отрасль изучает множество других альтернативных архитектур памяти. Среди них технологии MRAM, FeRAM, NRAM, RRAM, STT-RAM, PCM и другие. Эти новые битовые ячейки памяти предлагают уникальные компромиссы по сравнению со SRAM, такие как более высокая плотность при более низких характеристиках чтения/записи, возможности энергонезависимости, более быстрый цикл чтения-записи или меньшее энергопотребление.

Хотя перечисленные технологии они не являются прямой заменой SRAM, в будущем на их основе можно будет создавать кэш-память четвертого или пятого уровней, в которых снижение производительности может быть компенсировано более высокой плотностью.

DigiTimes: TSMC будет продавать пластины с 3-нм микросхемами за $20 000 — на 25% дороже 5-нм пластин

Источники: WikiChip Fuse, TechSpot